- 您现在的位置:买卖IC网 > Sheet目录3841 > TS80C31X2-LIE (Atmel)IC MCU 8BIT 30/20MHZ 44-VQFP

36

4428E–8051–02/08

AT/TS80C31X2

14.5.4

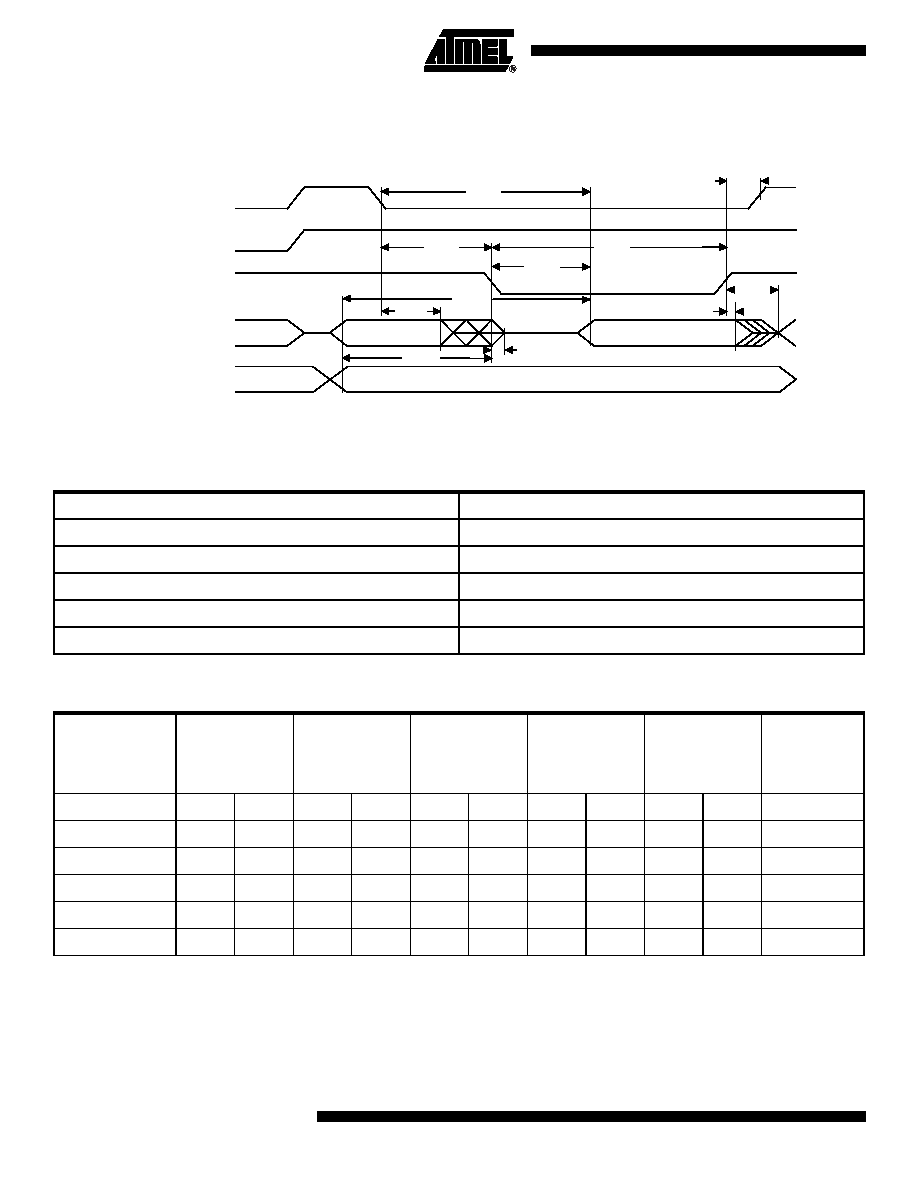

External Data Memory Read Cycle

Figure 14-8. External Data Memory Read Cycle

Table 14-11. Serial Port Timing - Shift Register Mode

Table 14-12. AC Parameters for a Fix Clock

ALE

PSEN

RD

PORT 0

PORT 2

A0-A7

DATA IN

ADDRESS

OR SFR-P2

TAVWL

T

LLWL

T

RLAZ

ADDRESS A8-A15 OR SFR P2

T

RHDZ

T

WHLH

T

RLRH

TLLDV

TRHDX

TAVDV

T

LLAX

T

RLDV

Symbol

Parameter

T

XLXL

Serial port clock cycle time

T

QVHX

Output data set-up to clock rising edge

T

XHQX

Output data hold after clock rising edge

T

XHDX

Input data hold after clock rising edge

T

XHDV

Clock rising edge to input data valid

Speed

-M

40 MHz

-V

X2 mode

30 MHz

60 MHz equiv.

-V

standard mode 40

MHz

-L

X2 mode

20 MHz

40 MHz equiv.

-L

standard mode

30 MHz

Units

Symbol

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

T

XLXL

300

200

300

400

ns

T

QVHX

200

117

200

283

ns

T

XHQX

30

13

30

47

ns

T

XHDX

0

ns

T

XHDV

117

34

117

200

ns

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

TS87C54X2-MCE

IC MCU 8BIT 16K OTP 40MHZ 44VQFP

PIC18F66K90-I/MR

IC MCU 8BIT 64KB FLASH 64QFN

PIC24HJ32GP304-I/ML

IC PIC MCU FLASH 32K 44-QFN

PIC18F67K22-I/PTRSL

MCU PIC 128K FLASH XLP 64TQFP

PIC18F66K90-I/MRRSL

MCU PIC 64K FLASH MEM XLP 64QFN

PIC16LC621-04/SO

IC MCU OTP 1KX14 COMP 18SOIC

PIC18LF2410-I/SP

IC MCU FLASH 8KX16 28-DIP

DSPIC30F3013-20I/SP

IC DSPIC MCU/DSP 24K 28DIP

相关代理商/技术参数

TS80C31X2-LIEB

制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:8-bit CMOS Microcontroller 0-60 MHz

TS80C31X2-LIED

制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:8-bit CMOS Microcontroller 0-60 MHz

TS80C31X2-LIER

制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:8-bit CMOS Microcontroller 0-60 MHz

TS80C31X2-LLAB

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit CMOS Microcontroller ROMless

TS80C31X2-LLAD

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit CMOS Microcontroller ROMless

TS80C31X2-LLAR

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit CMOS Microcontroller ROMless

TS80C31X2-LLBB

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit CMOS Microcontroller ROMless

TS80C31X2-LLBD

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit CMOS Microcontroller ROMless